# ELECTRONICS

VOLUME 19, NUMBER 1, JUNE 2015

# FACULTY OF ELECTRICAL ENGINEERING UNIVERSITY OF BANJA LUKA

Address: Patre 5, 78000 Banja Luka, Bosnia and Herzegovina Phone: +387 51 211824 Fax: +387 51 211408 Web: www.etfbl.net

# ELECTRONICS

Web: www.electronics.etfbl.net E-mail: electronics@etfbl.net

## Editor-in-Chief:

Branko L. Dokić, Ph. D. Faculty of Electrical Engineering, University of Banja Luka, Bosnia and Herzegovina E-mail: branko.dokic@etfbl.net

# Co Editor-In-Chief:

Prof. Tatjana Pešić-Brđanin, University of Banja Luka, Bosnia and Herzegovina E-mail: tatjanapb@etfbl.net

## International Editorial Board:

- Prof. Goce Arsov, St. Cyril and Methodius University, Macedonia

- Prof. Zdenka Babić, University of Banja Luka, Bosnia and Herzegovina

- Prof. Petar Biljanović, University of Zagreb, Croatia

- Prof. Milorad Božić, University of Banja Luka, Bosnia and Herzegovina

- Prof. Octavio Nieto-Taladriz Garcia, Polytechnic University of Madrid, Spain

- Dr Zoran Jakšić, IHTM, Serbia

- Prof. Vladimir Katić, University of Novi Sad, Serbia

- Prof. Tom J. Kazmierski, University of Southampton, United Kingdom

- Prof. Vančo Litovski, University of Niš, Serbia

- Dr Duško Lukač, University of Applied Sciences, Germany

- Prof. Danilo Mandić, Imperial College, London, United Kingdom

- Prof. Bratislav Milovanović, University of Niš, Serbia

- Prof. Vojin Oklobdžija, University of Texas at Austin, USA

- Prof. Predrag Pejović, University of Belgrade, Serbia

- Prof. Ninoslav Stojadinović, University of Niš, Serbia

- Prof. Robert Šobot, Western University, Canada

- Prof. Slobodan Vukosavić, University of Belgrade, Serbia

- Prof. Volker Zerbe, University of Applied Sciences of Erfurt, Germany

## Secretary:

Mladen Knežić, M.Sc. Željko Ivanović, M.Sc.

## Publisher:

Faculty of Electrical Engineering, University of Banja Luka, Bosnia and Herzegovina

Number of printed copies: 100

# Fast carrier recovery in FHSS systems with DDS based Costas loop

#### Slavko Šajić

Abstract—Owing to fast change of carrier frequency, the usage of coherent demodulation methods in Frequency-Hopping Spread Spectrum (FHSS) communication systems is limited by the coherent state acquisition performed by the local oscillator. To get around this difficulty, it is needed to implement the circuit within the FHSS system that is able to rapidly generate a coherent carrier. The work presented in this paper proposes a realization of Costas loop based on a combination of Direct Digital Synthesis (DDS), (Temperature-Compensated) Voltage-Controlled Oscillator ((TC)VCXO), and Phase-Locked Loop (PLL), which in particular enables a short period (less than 100 µs) required for a local oscillator to reach the coherent state. The implemented model is thoroughly described with measurements results also provided.

Index Terms—Costas loop, DDS, PLL, carrier, FHSS.

Original Research Paper DOI: 10.7251/ELS1519003S

#### I. INTRODUCTION

THE carrier signal synchronization is prerequisite for an application of a coherent demodulation method. In coherent communication systems, the technique of carrier synchronization is what drives the receiver structure. In general, there are two types of carrier synchronization techniques.

First type relies on a closed-loop phase which automatically tracks the carrier phase and use error feedback control to minimize the error in the received signal. Costas loop is most commonly used type of a closed-loop for carrier recovery [1]-[4]. This loop is not only adequate for a phase-based tracking of a suppressed carrier, but also for a demodulation of received signals. Therefore, the term 'Costas demodulator' is quite broad. Costas loop can be either analog or digital.

Second type relies on an open-loop phase with direct

Slavko Šajić is with the Faculty of Electrical Engineering, University of Banja Luka, Banja Luka, Bosnia and Herzegovina (e-mail: sajic@etfbl.net) estimation of a phase error. Open-loop phase and frequency synchronization schemes are based on either the Maximum Apriori (MAP) or Maximum Likelihood (ML) parameter estimation principles. These are general feedforward techniques where the signal parameter is actively estimated and then treated as statistic for a detection algorithm [5].

The feed-forward compensation algorithm with direct phase offset estimation using in-phase and quadrature-phase demodulator outputs is presented in [6]. The feedback compensation algorithm with carrier synchronization that compensate a phase offset using the feedback loop, and signal conversion to baseband performed by the receiver, is described in [7]. Lately, turbo synchronization time and frequency based methods have emerged. Turbo synchronization using an iterative Expectation-Maximization (EM) algorithm used to estimate carrier phase, frequency offset or timing within a turbo receiver is proposed in [8]. More specifically, carrier phase estimation within a turbo receiver in BPSK (Binary Phase Shift Keying) and QPSK (Quadrature Phase Shift Keying) systems is described in [9]. Turbo decoders involve significant mathematical operations which restricts their use in FHSS systems. Previously mentioned techniques use either feedback-loop with very small noise bandwidth or feedforward schemes which use training-sequences or symbol sequences in order to perform the time and frequency synchronization. These techniques might have relatively long acquisition time, and are not adequate for carrier synchronization in systems with short data packets.

Previous analysis demonstrates that fast carrier recovery has not been prioritized research activity. The fact that FHSS systems almost exclusively use incoherent demodulation methods proves our statement. Unlike the related work, this paper proposes a solution based on Costas loop, which enables fast carrier recovery. Proposed and implemented solution has the potential to be used for coherent demodulation in FHSS systems.

#### II. PROPOSED MODEL

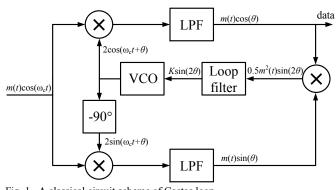

Costas loops are being used in analog and digital communication systems for carrier synchronization. Moreover, Costas loop can be used for carrier recovery from doublesideband suppressed carrier signals. A circuit scheme of classical Costas loop used for coherent demodulation of BPSK

Manuscript received 1 June 2015. Accepted for publication 15 June 2015. This article partially presents results from the PhD thesis "Contribution to the synchronization of radio communication systems in the channel with high error probability" defended at the Faculty of Electrical Engineering, University of Banja Luka.

Fig. 1. A classical circuit scheme of Costas loop. signals is shown in Fig 1.

The input signal is RF BPSK modulated signal  $m(t)\cos(\omega_c t)$ , which is a product of the transmitted data  $m(t)=\pm 1$  and the high frequency carrier  $\cos(\omega_c t)$ , where  $\omega_c = 2\pi f_c$ , and  $f_c$  denotes input signal carrier frequency. The sinusoidal voltagecontrolled oscillator (VCO) signal is represented by  $2\cos(\omega_c t + \theta)$ , where  $\theta$  is an implicit time function representing the portion of total signal phase not included in  $\omega_c t$ . On the upper branch the input signal is multiplied by the output signal of VCO, and signal  $m(t)\cos(\theta)$  is obtain at the output of lowpass filter (LPF). On the lower branch the input signal is multiplied by the VCO signal, shifted by -90°, and then lowpass filtered obtaining the signal  $m(t)\sin(\theta)$ . Signal of form  $0.5m^2(t)\sin(2\theta)$  is obtained after both branches being multiplied together. This signal is then filtered by the loop filter in order to provide control signal  $K\sin(2\theta)$ , which is used to adjust VCO frequency to the frequency of the input signal carrier. By reducing the phase error to zero, the VCO signal is synchronized with the carrier, and demodulated data are obtained on the upper branch. Thorough analysis of Costas loop with the noise influence on the loop performance can be found in technical literature.

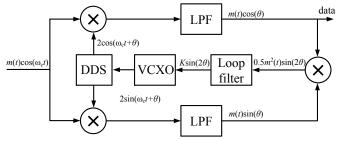

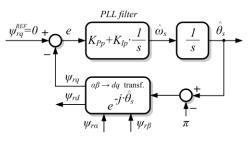

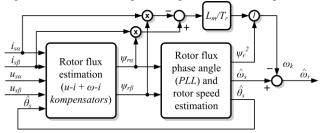

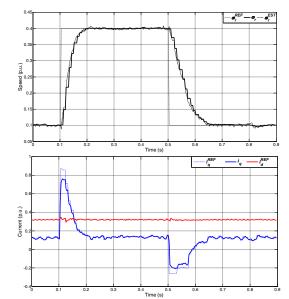

The proposed Costas loop is based on direct digital frequency synthesis (DDS) and voltage-controlled crystal oscillator (VCXO), as shown in Fig. 2. The VCO and phase shifter in the classical model given in Fig. 1, is replaced by DDS and VCXO. The VCXO or temperature-compensated voltage-controlled crystal oscillator (TCVCXO) is used as a reference clock for DDS. The TCVCXO is more temperature stabile than VCXO resulting in a lower frequency mismatch between the input signal carrier and DDS output signal. Therefore, this configuration has a lower acquisition time. In addition, DDS allows faster frequency change when used as a local oscillator (LO). It can output two signals whose frequencies and phase difference can be adjusted with very high resolution (order of mHz and less than degree, respectively). Due to high frequency and phase resolution, inphase and quadrature-phase signals can be provided by a single DDS chip.

The main advantage of this model of Costas loop is the ability to generate very fast and precisely both in-phase and quadrature-phase signals in complete DDS operating range.

Fig. 2. A circuit model of Costas loop based on DDS and VCXO.

This allows the usage of Costas loop in reconfigurable radio and FHSS systems. In-lock state of the Costas loop is achieved when there is no frequency and phase mismatch between input signal and DDS output signals.

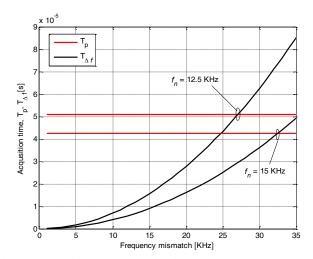

Considering fixed frequency scenario, the mean acquisition time  $T_{acq}$  consists of phase recovery time  $T_p$  and frequency recovery time  $T_{\Delta f}$  [10]. For the second order PLL, it is given by

$$T_{acq} = T_p + T_{\Delta f} = \frac{4}{\omega_n} + \frac{4.2(\Delta f)^2}{B_L^3}.$$

(1)

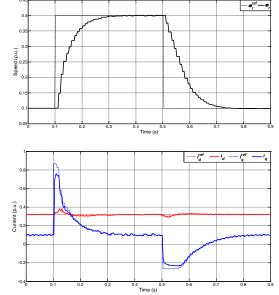

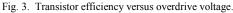

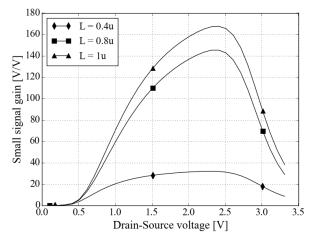

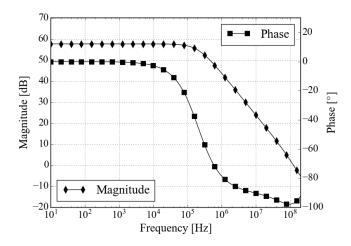

where  $\omega_n$  denotes PLL's natural frequency,  $B_L$  is PLL's bandwidth, and  $\Delta f$  is initial frequency mismatch. One can see that the frequency recovery time is proportional to the square of frequency mismatch. Phase and frequency recovery (locking) times as a function of frequency difference between the input signal carrier and local carrier are given in Fig 3.

Practical VCOs can have frequency mismatch of several kHz or MHz, which would have negative impact on frequency acquisition time. When there is no input signal, TCVCXO will oscillate at the frequency of crystal oscillator. Due to its relatively high temperature stability (0.28-2 ppm), DDS can be set very close to nominal frequency of the input signal carrier. This way, during the acquisition process, TCVCXO will reduce the frequency mismatch very fast, while phase recovery time would depend on natural frequency  $\omega_n$ . For example, considering TCVCXO with frequency stability of ±1 ppm and

Fig. 3. Phase and frequency acquisition times.

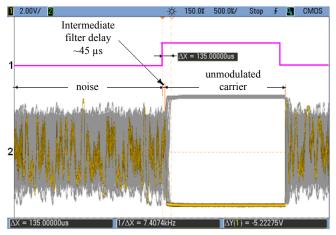

Fig. 4. Coherent state acquisition in Costas loop.

nominal frequency of 100 MHz, maximal frequency difference between the input signal carrier and local carrier is  $\Delta f = 200$ Hz. For the second order PLL with natural frequency  $f_n \approx 12.5$ KHz, damping factor  $\xi \approx 0.7$ , and  $B_L = \omega_n/2(\xi+1/4\xi) \approx \pi f_n =$ 39.2 KHz, time need to reduce frequency error can be assumed negligible, while mean phase acquisition time is 51 µs. Frequency recovery time gets higher with the increase of frequency difference, and becomes the same as phase recovery time for  $\Delta f = 27$  KHz. With further increase of input signal carrier and local carrier frequency mismatch, the frequency recovery time becomes larger than phase recovery time.

The above analysis is referred to the fixed frequency scenario. In frequency agile systems, such as FH radios, where an agile local carrier is required, maximal frequency mismatch is equal to overall available bandwidth. In this case, if VCO is used as a local oscillator, frequency acquisition time would be very high. However, in the model with DDS and TCVCXO, the frequency acquisition time is negligible compared to the time needed for phase recovery. Using higher natural frequency, thus allowing additional noise, one can reduce the loop-locking time. However, more noise power is causing abrupt change of phase of local carrier during the transmission, which further causes change of polarity of demodulated signal. Therefore, PLL should have greater natural frequency during

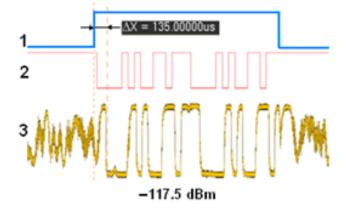

Fig. 5. The control signal (1), sequence (2) and demodulated signal (3).

Fig. 6. BER as a function of  $E_b/N_0$ .

the acquisition and a lower natural frequency afterwards. However, a proper moment of switching from one value of natural frequency to another is not an easy task, especially at low signal-to-noise ratios, which may be the subject of a future research.

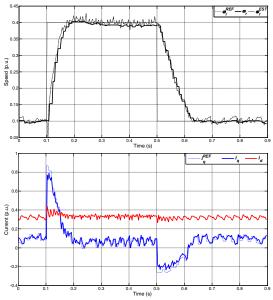

#### III. MEASUREMENTS RESULTS

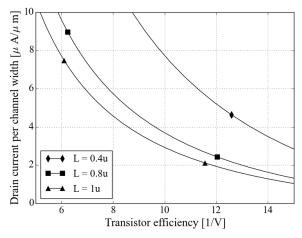

Fig. 4 shows PLL coherent state acquisition time with natural frequency  $f_n \approx 12.5$  KHz and damping factor  $\xi \approx 0.7$ . In order to measure the time period of interest, an input burst on-off keying (OOK) signal is used, as well as the VCXO. Signal 1 in Fig. 4 represents the modulating signal, whereas signal 2 represents in-phase component of demodulated signal in Costas loop. As notable from the figure, carrier demodulation is finalized within 135 µs. Reducing this value by the 45 µs delay of an intermediate frequency filter, one gets the coherent acquisition time of Costas loop. Given the aforementioned parameters and the frequency mismatch between the local and received signal of  $\Delta f = 1$  KHz, the time needed to acquire coherent state (acquisition time) is less than 100 µs.

Fig. 5 shows demodulated signal when RF signal level is set to -117.5 dBm. The modulating signal is given in a form of the short pseudo random (PN) sequence, making the receiving RF signal in a form of a burst signal, which is quite typical for radars and FHSS systems. For proper demodulation of first receiving bits from the PN sequence, it is required that the phase loop is in its coherent state. This means that the transmitter should start emitting the carrier before information data (or sequence) is being sent.

Minimal carrier emitting time corresponds to loop-locking time (acquisition of coherent state), which is less than 100  $\mu$ s, as stated before. It is demonstrated that the fast carrier generation at the transmitter is feasible [11], while keeping the phase noise and spurious signals at low level.

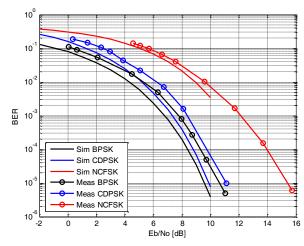

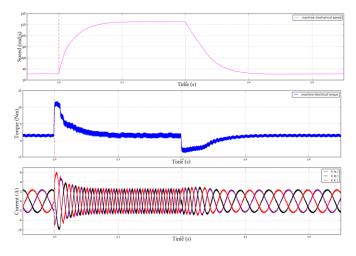

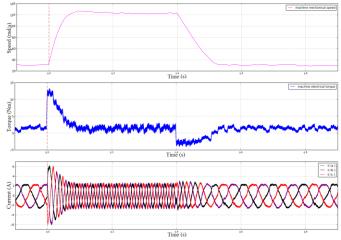

Theoretical and measured bit-error-rate (BER) as a function of signal-to-noise ratio  $(E_b/N_0)$  for BPSK, Coherent Differential PSK (CDPSK), and incoherent Frequency Shift Keying (FSK) is shown in Fig. 6. Measured BER for BPSK modulated signal is slightly worse relative to the theoretical BER for BPSK modulated signal ( $\leq 1$ dB). Nonetheless, Fig. 6 illustrates that coherent demodulation of BPSK modulated signal significantly outperforms incoherent demodulation of FSK modulated signal. As we already stated, to reduce the acquisition time, it is required to broaden the loop bandwidth (larger  $\omega_n$ ). However, this leads to an increased power of the noise. The trade-off between the time of the coherent state acquisition and BER might be in usage of the coherent detection of the differential PSK (CDPSK) signal, whose theoretical and measurements results are presented in Fig. 6. Due to the difficulties observed in carrier phase tracking in FHSS communication system, incoherent FSK and Binary Frequency Modulation (BFM) are mainly deployed. Using BPSK modulation technique in these systems, however, requires extremely fast acquisition time at the beginning of each hop interval.

#### IV. CONCLUSION

In this paper a model of the Costas loop based on direct digital synthesis and phase-locked loop has been proposed and analyzed. Results of the measurement have confirmed a high performance of the model in terms of acquisition time and biterror-rate at low signal-to-noise ratios. The proposed model has showed a very fast carrier recovery time (less than 100  $\mu$ s), and when combined with CDPSK modulation, it allowed coherent demodulation in FH radios. CDPSK had up to 3-4 dB better performance by means BER relative to NCFSK. Finally, the proposed model of carrier synchronization can be applied in reconfigurable radio systems.

#### REFERENCES

- R. E. Siferd and K. Xue, Costas Phase Locked Loop for BPSK Detection, Wright State University, 2008.

- [2] B. Shamla and D. Gayathri, "Design and Implementation of Costas Loop for BPSK demodulator", IEEE India Conference (INDICON), 2012.

- [3] M. Roddewig, S.A. Zekavat and S. Nooshabadi, "Design of a Costas loop downconverter", in 52. IEEE International Midwest Symposium on Circuits and Systems (MWSCAS'09), pp. 244-247, 2-5 Aug. 2009.

- [4] Z. Yang, Y. Bai, Z. Zhao, "Design and Implementation of the Digital Costas Loop Based on Software Defined Radio", First International Conference on Instrumentation Measurement, Computer, Communication and Control, 2011.

- [5] S.P. Nicoloso, An Investigation of Carrier Recovery Techniques for PSK Modulated Signals in CDMA and Multipath Mobile Environments. Blacksburg, Virginia, June 1997.

- [6] M. Nezami. Synchronization in Digital Wireless Radio Receivers. Florida Atlantic Univ., Doctoral dissertation, May 2001.

- [7] Y. Liuand and C. Tao, "Feedback Compensation Algorithm for BPSK/QPSK Carrier Synchronization", Radio Engineering, vol. 19, no. 1, pp.149-154, 2010.

- [8] N. Noels, C. Herzet, A. Dejonghe, V. Lottici, H. Steendam, M. Moeneclaey, M. Luise, and L. Vandendorpe, "Turbo Synchronization: an EM Algorithm Interpretation," in Proc. IEEE ICC, Vol. 4, pp. 2933-2937, May 2003.

- [9] L. Zhang and A. G. Burr, "Iterative Carrier Phase Recovery Suited to Turbo-Coded Systems," IEEE Trans. Wireless Comm., Vol. 3, pp. 2267-2276, Nov. 2004.

- [10] V. Manassewitsch, Frequency Synthesizers Theory and Design, Third Edition, New York, N.Y., John Wiley and Sons, 1987

- [11] S. Šajić, N. Maletić, M. Šunjevarić and B. Todorović, "Hybrid DDS-PLL Frequency Synthesizer with Reference Clock Modulation", Frequenz, Vol. 67, No. 7–8, pp. 233–236, 2013

# Modeling Method of Finite Element Modeler and Electromagnetic Solvers for Education and Research in RF MEMS

Tejinder Singh, Wael M. El-Medany and Kamal J. Rangra

Abstract-Field of electronics engineering is the most captivating among students, researchers and academicians now-adays. With the passage of time the requirement of advance tools for engineering is increasing. Many institutions and universities around the globe provide quality education to various engineering domain. Students although study theory courses but they also need exposure that how theory can be related to actual devices. Simulations play an important role for relating theoretical components to the virtual practical environment. Students of Radio Frequency (RF) domain and especially students that are studying Microelectromechanical Systems (MEMS) as courses, due to the extreme complexity of these devices, students need multiple tools to simulate the performance parameters. This paper highlights the most prominent tools that are used in the industry to design and implement RF MEMS structures. The role of Electromagnetic (EM) solvers and Finite Element Modeller (FEM) and its impact on electronics engineering education is demonstrated. Modeling approach of these tools are also explained. These tools and due to there huge advantages, electronics graduates should study these tools in their course curriculum to know how to tackle various types of RF problems and through case studies, it is demonstrated that how these tools can aid shift from just theoretical study to virtual practical environment.

*Index Terms*—EM solver, FEM, electronics engineering, education, simulation environment.

Original Research Paper DOI: 10.7251/ELS1519007S

#### I. INTRODUCTION

**M**ANY a times, graduate engineering students or graduate research students face variety of challenges in designing and modeling the problems that are spanned in multiple disciples of engineering and applied sciences [1]. Streamlined computational methods and techniques that combine the technologies and that can handle engineering problems are required to precisely model the issues and accurately predict results before manufacturing or fabrication [1], [2]. Most of the electronic engineering programmes offer domain specific simulation and modeling methods on a very limited basis.

Manuscript received 16 November 2014. Received in revised form 15 February 2015. Accepted for publication 16 March 2015.

Tejinder Singh is an Assistant Professor in MEMS and VLSI Architectures Domain under Discipline of Electronics and Electrical Engineering, Lovely Professional University, Phagwara 144 402, PB, India, (*Corresponding Author* - Ph: +91 - 988 (800) 9896, Email: tejinder.singh@ieee.org).

Dr. Wael M. El-Medany is a Professor in Department of Computer Engineering, College of Information Technology, University of Bahrain, Zallaq, Kingdom of Bahrain.

Dr. Kamal J Rangra is a Chief Scientist, Professor AcSIR and in Semiconductor and Micro/Nano Fabrication Laboratory, CSIR-CEERI (Central Electronics Engineering Research Institute), Pilani 333 031, RJ, India.

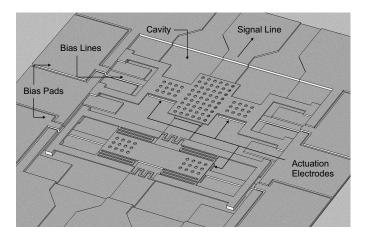

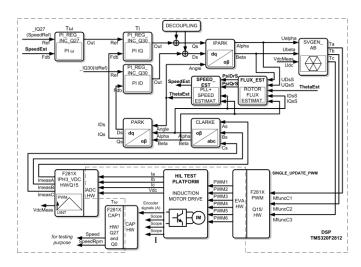

Fig. 1. T. Singh [5] proposed the RF MEMS switch based on series-shunt configuration, both membranes are incorporated inside the cavity. Bias pads demonstrate the actuation signal routing beneath the membranes. [Copyright © 2014, Springer Science, NY]

Our primary focus is on group of graduates that are into RF MEMS/antenna designing. RF MEMS [3] is a very fast growing field of research. Students usually face challenges in modeling and simulating RF MEMS systems [4]. We have encountered many questions on technology forums and through emails, students that just entered into this industry wonder that which tools are most prominent for simulating these micro structures.

Fabricating RF MEMS devices [6], [7] is a cumbersome process, hence simulations is the best bet to get approximate near to actual response. Theoretically it said that RF MEMS systems show excellent performance like high isolation and low insertion loss. But, to model the response, complex mathematical derivations need to be solved prior to check performance. EM solvers, provide comprehensive solution to all these RF or microwave related issues. Including, radiation field analysis, near and far fields, S, Y and Z parameters to name a few. If taught as core curriculum with hands on experience with these tools, fresh grads can usher in the industry. FEM on the other hand solves multi domain physics problems and provide solutions as per the requirement. Hence, companies are now opting for multi-physics modeling or finite element modeller (FEM) [8], [9] to save costs and to reduce computing resources. One tool can handle various physics problems. By this way, students not only learn their field specific solvers, instead they also get experience to couple various

physics problems that may include, particle trajectories, flow analysis, damping analysis, stress or fracture analysis, doping concentration, charge flow and many more. Universities should focus on these issues and add finite element modeling in the course curriculum of graduate engineering students [2], [10].

Basically, FEM environment require the basic knowledge of the problem that one is going to tackle as a prerequisite. Once, the governing equations of the problem is provided, then using FEM computation methods, the FEM, thus ask for boundary conditions and finally computes those governing equations for specified boundary conditions [1], [4], [11], [12]. It takes a very little time if the basics are strong and clear. EM solvers are a boon to RF engineers, couples with FEM is just icing on the cake. These tools takes the theoretical inputs and do all the simulation and testing in between the framework of theory to actual development.

Engineering curricula in good universities offer design and research experience of various tools to better teaching and practical exposure. An electronics graduate student may require FEM techniques to solve electric field issues as well as overall device level issues like mechanical stresses or chemical process if the system is on same chip or base. This paper presents the need of these tools as an electronics engineering graduate course curricula that should covers the most of the methods and techniques relating to theory courses [11], [12].

Mostly, graduate engineering students become active participants in concept based learning than their theory counterparts. More generally, These tools not only teach them how to solve physics problems but also make them understand in very efficient manner. The introduction of the concept (need of simulation methods as a course) is explained in introduction followed by a section on impact of research tools on education and core technologies behind these tools. The statements are supported by our prior research work, by providing two case studies, in which Section IV, covers RF performance simulation using commercially available EM solvers followed by Section V, that reports the use of FEM on the design and analysis of RF MEMS. We have provided simulation process flow in Section III as well. The concluding remarks are given in Conclusion section.

#### II. IMPACT OF RESEARCH TOOLS ON EDUCATION AND CORE TECHNOLOGIES

There are many industrial grade tools for simulation depending on the problems. Now-a-days, tools are developed that we can also couple the physics from different domains for analysis [4], [13]. Modeling tools provides an environment for engineers in which they can design, analyse/simulate, compare the results and optimise various factors depending on the type of application [14]. Students after their engineering education, definitely look for engineering jobs. It is always advantageous for students to learn and practise these tools in whichever field they want to pursue their careers [15].

Our primary focus of this paper if for the graduates, who are studying antennas, RF engineering, microwave engineering, microelectromechanical systems or micro systems course in their curriculum, can get advantage to implement the theoretical designs and concepts in these tools. Thus by this methodology and practise graduates not only learn in an efficient manner, but also can understand better and comply with the industry requirements. Many a times, students face the issues that what to do with the mathematical formulas, that they are studying as theory [15]. Even in our classes, during lecture delivery, we show them the simulations that how those mathematics come into picture when we solve real world problems.

Universities might not have industrial grade testing labs or research centres, but either a lab related to the research tools or simulations along with lecture delivery can make students learn and understand in an efficient way. As, we have implemented this methodology from last few months, we have seen that students now learn and understand mathematical concepts in better way. They remember the things if we relate it to real world problems.

In this paper, we provided two case studies, that clearly relates the use of engineering tools, specially EM solvers and FEM in the field of Antennas, microwave theory and the most prominent research area RF MEMS.

#### A. Aid of Simulation Tools

As discussed in the previous section, we have designed an RF MEMS switch and relating the computed parameters from mathematical formulas to implementing in EM solver and FEM to check how accurate these tools are and how these tools can save abundant of time.

Solving partial derivatives and many other complex mathematical equations are not practical for engineering field. Such tools provide, ready to use solving algorithms and provide the results that are very close to the actual solutions. Simulations act as a mid way in between theory to development. It plays a very crucial role, providing ample space to optimise and check the solution to the problem.

In RF industry, performance and size of the devices are limiting factor especially for RF MEMS [16], [17]. For RF MEMS Switches, scattering parameters are analysed to check its RF performance. Other that that we are interested in how E field and H field of RF signal travels in the RF MEMS switches or subsystems. Then there comes the analysis of current density, *J*, temperature, leakage, resistant, capacitance, inductance, q-factor to name a few. That can be easily simulated in commercially available EM solvers like Ansys HFSS, Sonnet, CST Microwave Studio, EM3D and many more. These are many different types of EM solvers available in the market based on requirements.

Then to check the issues like stress gradient, voltage requirement, spring constant, switching time, damping, fracture analysis etc, finite element modeller are used. FEM like COMSOL or Ansys Workbench provides sophisticated solution in a close proximity to the real world fabricated designs. FEM divides the problem into finite elements of very small or desired size called the *Mesh* and solve the governing equations relating to that particular problem.

Fabricating RF MEMS switches and subsystems needs million dollar machinery, time, knowledge and engineering. Hence, these tools before going into actual experiment or fabrication run, provides relatively exact solutions. That saves time and money, thus increase productivity.

Students, if they would be knowing the tools before entering into industry, they can perform better and their initial performance in industry would be impactful on peers.

Briefly, in the following sections, we have presented the Series-Shunt based RF Switch, we have analysed the RF performance and Stress distribution. The comprehensive study of the RF MEMS switch is given in [5]

#### III. SIMULATION PROCESS FLOW AND DESIGN PROPERTIES

Till now, We have discussed that simulation represent an invaluable link between theory and practice in modern engineering. In this section, the simulation process flow is demonstrated.

#### A. Process Flow using Ansys HFSS

1) Geometry: Geometry can be created in 3D environment layer by layer. After setting the units to appropriate scale, one can start designing the geometry of product (RF MEMS Switch as used in this case). Geometry can be imported or exported in variety of formats to exchange with different simulation tools.

2) *Material Assignment:* After creating the geometry, material has to be assigned to different layers, as an example, bulk of Silicon (Si), is used mostly followed by a deposition of dielectric layer of different material. Once the material selection is complete, one can proceed to next section.

*3) Ports Excitation:* I/O Ports have to be assigned. We have to design the CPW lines to characterise it for 50 ohm for ease in coupling with coaxial cables. In this case study, typically for RF MEMS Switch, we have used Port 1 and Port 2 as input and output port with Wave Port assignment to both ports.

4) Analysis Setup: After setting up the model, we have to setup analysis. We have provided a linear frequency sweep of DC to 40 GHz with step size of 0.1 GHz to simulate RF performance of the designed switch. We have used smaller step size to get precise results. Although, less the step size, can affect computation time. Although, this tool provides the provision of High performance computing concept, such that we can use all the licenses available with us to get results in less time. Parts of the projects is usually simulated by using the computation power of different machines and then it automatically combine the results in host machine.

5) Checking the Results: After the completion of analysis, results can be plotted using Rectangular 2D plot option. Then, we can easily check the performance of switch while plotting S11 as Return loss [dB] and S21 as Isolation [dB] of the switch.

#### B. Process Flow using COMSOL Multiphysics

Although, Multiphysics environment provides, realistic approach to solve various physics problems. We can couple the physics to get best of both worlds. But, just to highlight the advantage of EM solver, we have simulated RF performance in Ansys HFSS and mechanical modeling in COMSOL

Multiphysics. RF performance can also be simulated using COMSOL Multiphysics only. But, from our experience, it takes much more time to compute the same problem, thus we have chosen HFSS as our dedicated EM Solver.

1) Geometry: We have to check the mechanical issues like stress gradient, spring constant and pull-in voltage required to deflect the beam for particular gap height,  $g_0$ . We have to set the units to micrometers. In this, we need only metal membrane instead of complete geometry to ease the computational load. Hence, we imported membrane only in multi physics environment to start investigating the issues further.

2) Material Assignment: In COMSOL, huge library of materials is already provided with details like Poisson Ratio, Elasticity, Permittivity, Permeability, Density, Young's modulus, thermal coefficient and many more. We then assigned "Au" material from category MEMS, as the only material for this switch membrane.

*3) Physics:* We have chosen, Electromechanics (emi) physics and stationary study for this particular problem. This physics allows to compute pull-in voltage and deflection of membrane.

4) Boundary Conditions: For this model, we have assigned inner membrane as Linear Elastic Material, while the fixed constraints are bottom side anchors of membrane. Then, we have to choose Boundary Load and we have applied boundary load as Contact Pressure as a predefined variable followed by Prescribed Mesh Displacement. At last, we have applied boundary conditions: Voltage Terminal and Ground Terminal.

5) *Mesh:* COMSOL Multiphysics offer physics controlled mesh depending on the complexity of geometry or we can optimise the mesh to reduce computation time. for this model, we have chosen Mapped mesh and Swept the mesh in complete geometry.

6) Solver: COMSOL offer variety of solvers, but we have optimised the solver for our model. We chose Full couples solver and under Method and Termination section, we chose Nonlinear method to select Automatic (Newton). Finally under "Direct" option, we chose PARDISO solver.

7) Computation and Results: After setting up the model, we computed it and plotted the results as desired in Results section. In that section, we can plot 3D, 2D or 1D results depending on the requirement.

The correctness of simulation results with experimental results can be seen from the work of [3], [18], in which researchers have fabricated the designs and compared the performance.

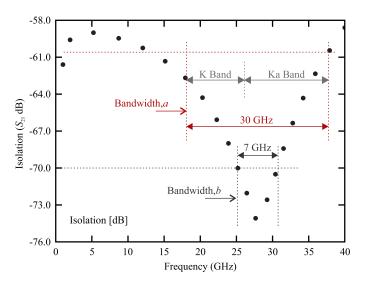

#### IV. CASE STUDY I - RF PERFORMANCE ESTIMATION USING EM SOLVERS

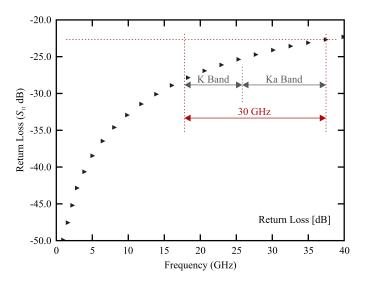

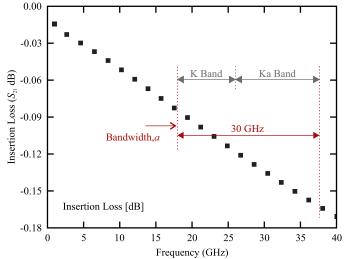

The most critical parameter for any RF system or device is to analyse its RF performance. RF performance is the most important factor that primarily shows the performance of MEMS that it is intended for. The isolation loss, return loss and insertion loss of the RF MEMS switch is simulated using commercially available EM solver Ansys HFSS. RF performance of the switch is observed between frequencies 1 to 40 GHz. Fig. 2 shows the peak isolation  $S_{21}$ , of 75 dB at 28 GHz in OFF state, although the switch has very large bandwidth of 30 GHz, i.e., it can be used for K–Ka band applications. From the results, the performance of switch is excellent for said frequency bands. Two bandwidths a and b are considered, Bandwidth a is 30 GHz and has the complete frequency range of K and Ka band that shows more than 60 dB of isolation and bandwidth, b is 7 GHz narrow bandwidth that shows excellent isolation of above 70 dB from 25 GHz to 32 GHz. The solution to the RF problems thus can easily be solved by using EM solver as demonstrated [19].

Numerically the S-parameters  $S_{11}$ ,  $S_{21}$  in both switching states can be computed using the Y and Z-matrix data from EM solver and by plugging the values in equations given below. To determine the ON state parameters,  $Y_{11-x}$ is required, where x = 1 for switch in ON state and x = 0for switch in OFF state.

$$S_{11-x} = \left(\frac{Y_z^2 - Y_{11-x}^2 + Y_{21-x}^2}{(Y_{11-x} + Y_z)^2 - Y_{21-x}^2}\right)$$

(1)

where  $S_{11-x}$  is the ON or OFF state return loss depending on the variable x,  $Y_z = 1/Z_0$ ,  $Y_{11-x} = j\omega C_{down}$  for x = 0 i.e., in OFF state and  $Y_{11-x} = j\omega C_{up}$  for x = 1 i.e., in ON state.  $Y_{21-x} = -j\omega C_{down}$  for x = 0 and  $Y_{21-x} = -j\omega C_{up}$  for x = 1 i.e., in OFF and ON state respectively. Isolation  $S_{21-0}$ and insertion loss  $S_{21-1}$  can be analysed by using

$$S_{21-x} = \left(\frac{-2Y_{21-x}^2Y_z}{\left(Y_{11-x} + Y_z\right)^2 - Y_{21-x}^2}\right)$$

(2)

For the switch in ON state, the return loss,  $S_{11}$  and insertion loss,  $S_{12}$  is computed. Fig. 3 shows the return loss of 24 dB and Fig. 4 shows low insertion loss of 0.13 dB at 28 GHz with markers for complete 30 GHz bandwidth for K and Ka bands.

Fig. 2. Simulation of Isolation [dB] performance for combined switch in series–shunt configuration. The simulation is done for frequency sweep of 1–40 GHz and results in maximum peak isolation of 75 dB at 28 GHz. Two bandwidths are considered for this switch, Bandwidth (a) 30 GHz is very large with above 60 dB of isolation and bandwidth (b) 7 Ghz has excellent isolation of above 70 dB. Parameters are for the RF MEMS switch shown in Fig. 1, courtesy T. Singh [5]

Fig. 3. Return loss [dB] for switch in series–shunt configuration. The simulation results are analysed for frequency sweep of 1-40 GHz and demonstrates the maximum peak return loss of 50 dB at 1 GHz and 24.5 dB at 28 GHz.

Fig. 4. Insertion loss [dB] simulation for complete switch in series–shunt configuration. The simulation is carried out for frequency sweep of 1-40 GHz and demonstrates the maximum peak insertion loss of 0.015 dB at 1 GHz and 0.13 dB at 28 GHz.

#### V. CASE STUDY II - FINITE ELEMENT MODELING FOR RF-MEMS

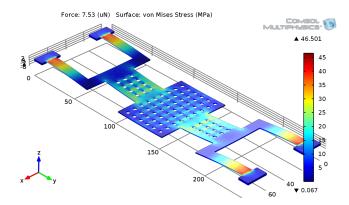

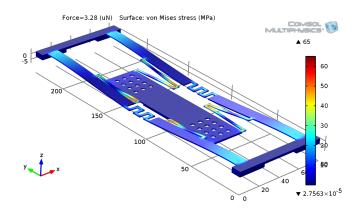

RF MEMS switches or subsystems are highly regarded for their better RF performance in microwave regime than their semiconductor counterparts. RF MEMS switches have huge advantage including; excellent isolation, low insertion loss, negligible power consumption, very compact structure, low cost of manufacturing [20]. But these tiny intelligent devices suffer from reliability issues including stiction and high voltage requirements [13], To overcome these problems, researchers and designers has to model and analyse the issues first and then optimise the design accordingly. In this case study, we have reported that how FEM is useful in estimating the stress gradient to help determining how the membrane of RF MEMS can handle stress for reliable operation [5].

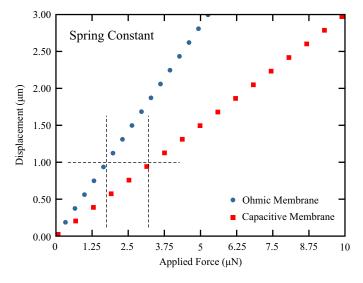

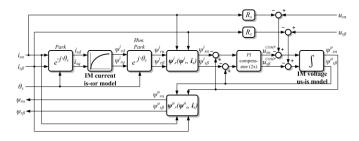

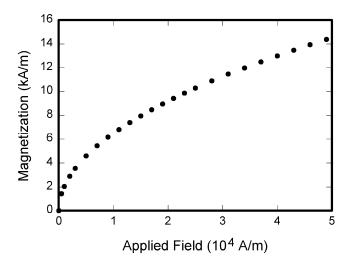

The design and modeling parameters are reported in [5], [20]. We have presented the stress analysis for two different membranes. We have also reported the spring constant estimation and pull-in voltage analysis of these switches by using FEM. Although, RF performance is analysed by EM solver and is given in the previous section. There is a need of FEM (Finite Element Modeling) to check various parameters before fabrication of devices [16]. For this proposed switch, the spring constant, stress and pull-in voltage required for actuation is analyzed as discussed in [5], [20]. COMSOL Multiphysics is used as finite element modeler for analyzing the parameters [17], [20]. This section deals with the coupled physics, electrostatic + magnetic problem solving. Analytical calculations of spring constant for complex structures are not possible, because the formulas presented till now are for simple beams or for beams with simple meanders. The complex geometries can be better analyzed using FEM. To calculate the spring constant and stress in membranes, sweep of force is applied over the area of electrodes. Both the membranes are analyzed one by one for the same force and displacement sweep.

As the membranes are made of gold, the gold can withstand stress of 100 MPa and it fails for values higher than that. The effective stress can be seen in membranes from Fig. 5 and

Fig. 5. Capacitive / Shunt switch membrane stress analysis for 2.5  $\mu$ m gap height, showing maximum stress of 46.5 MPa. [Copyright ©2014, Springer Science, NY]

Fig. 6. Results by T. Singh [5] Ohmic / Series switch membrane stress analysis for 3  $\mu$ m, showing maximum stress of 65 MPa. [Copyright ©2014, Springer Science, NY]

6 respectively. The von Mises stress analysis is mandatory to check the maximum stress level. If the maximum stress increases for a given gap height from the stress a material can withstand, then it is an alert for failure in design. But the redesigned membranes can withstand stress for assigned gap height and have margin to take twice of more stress. The ohmic membrane is designed to reduce the spring constant and stress. The side view of ohmic membrane is shown in Fig. 7. It depicts that the sides of membrane are not making any contact with signal line and it helps to keep the inner membrane straight for better contact and better switching speeds. It increases the reliability of switch as well. The spring constant for ohmic and capacitive switch membranes are shown in Fig. 8

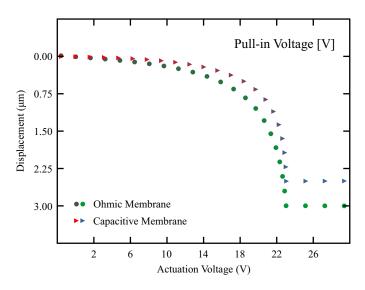

The actuation voltage is analyzed by plotting a curve of applied voltage vs. deflection of beam. The voltage required for desired gap height is shown in Fig. 9. The ohmic switch membrane works properly on 3  $\mu$ m gap and capacitive switch membrane on 2.5  $\mu$ m. The pull-in voltage required is same for both membranes as shown in plot.

Theoretically, determining the fundamental mode of operation is also required for certain analysis. The equation of motion of the thin metal beam that is under harmonic force is considered. In single degree of freedom, the harmonic motion of the mass-spring system is fundamentally modelled with the  $2^{nd}$  order differential equation as

$$m_{\rm eff} \frac{\mathrm{d}^2 x}{\mathrm{d}t^2} + \gamma_{\rm eff} \frac{\mathrm{d}x}{\mathrm{d}t} + k_{\rm eff} x = F_e \tag{3}$$

where  $m_{\rm eff}$  is the beam's effective mass,  $\gamma_{\rm eff}$  is the effective coefficient of damping of dielectric material,  $F_e$  is the electrostatic force and  $k_{\rm eff}$  is the effective spring constant.  $m_{\rm eff}$  is of gold material, effective mass of inner movable beam i.e., 8.52 ng. Effective spring constant  $k_{\rm eff}$  is composed of k' and k''. According to [3] the component of biaxial residual stress k'' can be neglected due to the crab type flexures design, perforation i.e., holes are added to release the biaxial residual stress in membrane.  $\gamma_{\rm eff}$  can be estimated by computing Eq. 3 by fitting all the remaining values.

The spring constant is simulated for the membrane and shown in Fig. 8. For the serpentine flexures, the numerical values of spring constant can be analysed by using

$$k' \approx \frac{48GJ}{l_a^2 \left(\frac{GJ}{EI_x} l_a + l_b\right) n^3} \quad \text{for } n \gg \frac{3l_b}{\frac{GJ}{EI_x} l_a + l_b} \quad (4)$$

where n is the number of meanders in the serpentine configuration, G = E/2(1+v) is the torsion modulus,  $I_x = wt^3/12$ is the moment of inertia, and the torsion constant is usually

Fig. 7. Vertical defection in ohmic switch membrane showing deflection in Z–direction, from this side–view image, the straight contact over signal line and contact area on electrodes can be seen.

Fig. 8. Spring contact analysis for ohmic and capacitive switch membranes for displacement sweep of  $0.3 - 3.3 \ \mu$ m vertical displacement in Z-direction

Fig. 9. Simulation of actuation voltage requirement by series and shunt membranes. The voltage is simulated for the maximum 3.5  $\mu$ m displacement. The maximum voltage required are optimized to use same potential for different gap height of 2.5  $\mu$ m for series and 3  $\mu$ m for shunt membrane.

given by

$$J = \frac{1}{3}t^{3}w \left(1 - \frac{192}{\pi^{5}}\frac{t}{w}\sum_{\substack{t=1,\\i=odd}}^{\infty} \frac{1}{i^{5}}\tanh\left(\frac{i\pi w}{2t}\right)\right)$$

(5)

The effective spring constant  $k_{\text{eff}}$  can be determined by plugging material values like Young's modulus E and moment of inertia  $I_x$  in Eq. 4. The combined spring constant  $k_{\text{eff}}$  for the membrane is 1.5 N/m for ohmic and 2.7 N/m for capacitive membrane.

The natural frequency of the membrane depends on the equivalent spring constant and the effective mass, the natural frequency  $f_0$  is given as

$$f_0 = \frac{1}{2\pi} \sqrt{\frac{k_{\text{eff}}}{m_{\text{eff}}}} \tag{6}$$

Next higher mode of eigenfrequency  $f_1$  can be determined by using

$$f_1 = \frac{1}{2\pi} \left[ \frac{15.418}{L^2} \right] \sqrt{\frac{EI_x}{\rho}} \tag{7}$$

where;  $\rho$  is the mass density (mass/length), L is length of membrane

#### VI. ASSESSMENT RESULTS

To check the understanding of concepts by introducing simulation environment to students, we have conducted a survey of 3 Grad classes and 2 Undergrad classes. While, teaching the subject RF MEMS theoretically, we have presented the simplistic flow of simulation and explained its use among students. They students first of all became more attentive in the class, and whatever they have learned using tools i.e., results computed using simulation environment were more regarded by students. A simple exercise of comparing the simulation results with analytical results provides a good method of learning among students. They started relating the numerical concepts in correct manner. By teaching using simulations, brain become more attentive to see the actual working of analytical equations on products/designs. Students tend to learn and understand things faster.

We have conducted a survey by demonstrating few simple electromagnetic related problems and their computed solutions by numerically and using computationally, and finally found that more than 90% of undergrad and grad students wanted faculty to teach using these kind of tools for their better understanding. We then taught about a simple physics problem numerically or analytically in one section consisting more than 60 students with their average academic standing of grade A. Simultaneously, we taught about same physics problem by introducing simulation tools to the students with average academic standing of grade B.

After that session, we conducted a test based on that problem and found the score of test of students taught using simulation tools scored way better than other section. Students enjoyed learning about the concepts if taught using computational tools.

#### VII. CONCLUSION

The role of EM solvers and finite element modeller for researchers in RF MEMS domain is discussed by citing two case studies from our previous research work. Our primary focus in this paper is to relate the industrial requirements to the electronics engineering students. Students who are working or want to work in antennas or RF MEMS industry can take advantage, if they would learn these tools in their course curriculum. The capabilities of these tools in solving engineering problem is demonstrated in both case studies. It is clear that the capabilities of these tools are tremendous for any cross-coupled physics problems. The learn curve might be steeper for some, but once mastered it cam drastically reduce the designing and testing time. As only engineers can develop efficient and advanced products that can serve the needs of humanity and it can be possible with the quality engineering education.

#### APPENDIX – I

Design parameters and material parameters are given in Table I and in Table II respectively for the RF MEMS switch designed for Case study in this paper. These parameters are for the design elaborated in depth by T. Singh [5]

TABLE I

Specifications of the RF MEMS switch

| Component              | Length<br>µm | Width $\mu m$ | Depth<br>µm | Material |

|------------------------|--------------|---------------|-------------|----------|

| Substrate              | 412          | 412           | 200         | Quartz   |

| Substrate Dielectric   | 412          | 412           | 0.5         | $HfO_2$  |

| CPW (G S G)            | 126          | 31.5          | 1           | Gold     |

| Cavity                 | 245          | 245           | 3           | _        |

| Series Membrane        | 235          | 80            | 1           | Gold     |

| Shunt Membrane         | 245          | 80            | 1           | Gold     |

| Electrode $\times 4$   | 35           | 40            | 1.5         | Gold     |

| Series Contact Pad     | 35           | 31.5          | 0.5         | Gold     |

| Meanders width         | A (10)       | B (3.5)       | C(2.5)      | Gold     |

| Signal Line Dielectric | 80           | $31.5^{'}$    | $0.25^{'}$  | $HfO_2$  |

In value column, first value is for ohmic membrane and second is for capacitive unless otherwise specified. The parameters are given in Table. II. Some parameters are given in the specification table as shown in Table. I.

TABLE II RF MEMS Switch – Materials Properties

| Parameter           | Notation        | Value                      |

|---------------------|-----------------|----------------------------|

| Young's Modulus     | E               | 70 GPa                     |

| Density             | ρ               | 19,300 Kg/m <sup>3</sup>   |

| Poisson's Ratio     | $\nu$           | 0.44                       |

| Dielectric Constant | $\varepsilon_r$ | 25                         |

| Spring Constant     | k               | 1.5, 2.7                   |

| Initial Gap         | $g_0$           | $2.5, 3.0 \ \mu m$         |

| Holes Radium        | $r_0$           | $3.8 \ \mu m$              |

| Mean Free Path      | $\lambda$       | 70 nm                      |

| Mass of Membrane    | m               | $8.52, 11.3 \ \mathrm{ng}$ |

#### REFERENCES

- K. Preis, O. Biro, T. Ebner, and I. Ticar, "An electromagnetic field analysis tool in education," *Magnetics, IEEE Transactions on*, vol. 38, no. 2, pp. 1317–1320, 2002.

- [2] I. Milanovic, T. Eppes, and I. Russell, "Engineering multiphysics research," *International Journal of Online Engineering (iJOE)*, vol. 7, no. 2, pp. pp–24, 2011.

- [3] G. M. Rebeiz, *RF MEMS: Theory, Design, and Technology*. John Wiley & Sons, 2004.

- [4] T. Eppes, I. Milanovic, and I. Russell, "Multiphysics modeling with high priority research applications," in *Global Engineering Education Conference (EDUCON)*, 2011 IEEE, 2011, pp. 59–64.

- [5] T. Singh, "Design and finite element modeling of series-shunt configuration based RF MEMS switch for high isolation operation in K-Ka band," *Journal of Computational Electronics*, vol. 14, no. 1, pp. 167– 179, 2015.

- [6] G. M. Rebeiz and J. B. Muldavin, "RF MEMS switches and switch circuits," *Microwave Magazine, IEEE*, vol. 2, no. 4, pp. 59–71, 2001.

- [7] G. M. Rebeiz, "RF MEMS switches: status of the technology," in TRANSDUCERS, Solid-State Sensors, Actuators and Microsystems, 12th International Conference on, 2003, vol. 2. IEEE, 2003, pp. 1726–1729.

- [8] COMSOL Multiphysics 4.4b Finite Element Modeler. Available at http://www.comsol.com/.

- [9] Ansys High Frequency Structure Simulator (HFSS). Available at: http://www.ansys.com/hfss.

- [10] J. Lu, "High performance computation and interactive visualization of electromagnetics for engineering education programs," *Magnetics, IEEE Transactions on*, vol. 48, no. 2, pp. 299–302, 2012.

- [11] R. Geike, T. Berlin, and V.-u. U. Maschinenbau, "COMSOL multiphysics in education-chemical reactions, heat and mass transfer," in *Proceedings of the COMSOL Conference*, vol. 1, Hannover, 2008.

- [12] K. Gupta, T. Itoh, and A. A. Oliner, "Microwave and rf educationpast, present, and future," *Microwave Theory and Techniques, IEEE Transactions on*, vol. 50, no. 3, pp. 1006–1014, 2002.

- [13] T. Singh and N. Khaira, "High isolation Single-Pole Four-Throw RF MEMS switch based on series-shunt configuration," *The Scientific World Journal*, vol. 2014, 2014.

- [14] E. M. Willis and G. R. Tucker, "Using constructionism to teach constructivism: Modeling hands-on technology integration in a preservice teacher technology course," *Journal of Computing in Teacher Education*, vol. 17, no. 2, pp. 4–7, 2001.

- [15] T. Singh, "From theory to development: Role of multiphysics modeling and its effect on education in electronics," *Electronics*, vol. 17, no. 2, pp. 105–109, 2013.

- [16] T. Singh, "Effective stress modeling of membranes made of gold and aluminum materials used in radio-frequency microelectromechanical system switches," *Transactions on Electrical and Electronic Materials*, vol. 14, no. 4, pp. 172–176, 2013.

- [17] T. Singh and F. Pashaie, "Circuit modelling and eigenfrequency analysis of a Poly-Si based RF MEMS switch designed and modelled for IEEE 802.11 ad protocol," *Journal of Computing Science and Engineering*, vol. 8, no. 3, pp. 129–136, 2014.

- [18] G.-L. Tan, R. E. Mihailovich, J. B. Hacker, J. F. DeNatale, and G. M. Rebeiz, "Low-loss 2-and 4-bit ttd mems phase shifters based on sp4t switches," *Microwave Theory and Techniques, IEEE Transactions on*, vol. 51, no. 1, pp. 297–304, 2003.

- [19] T. Singh and K. J. Rangra, "Compact low-loss high-performance singlepole six-throw RF MEMS switch design and modeling for DC to 6 GHz," *Microsystem Technologies*, pp. 1–10, 2015.

- [20] T. Singh and F. Pashaie, "Finite element modeling of a Ti based compact RF MEMS series switch design for harsh environment," *Microsystem Technologies*, pp. 1–7, 2014.

# Cost Effective Implementation of Fixed Point Adders for LUT based FPGAs using Technology Dependent Optimizations

Burhan Khurshid and Roohie Naaz

Abstract—Modern day field programmable gate arrays (FPGAs) have very huge and versatile logic resources resulting in the migration of their application domain from prototype designing to low and medium volume production designing. Unfortunately most of the work pertaining to FPGA implementations does not focus on the technology dependent optimizations that can implement a desired functionality with reduced cost. In this paper we consider the mapping of simple ripple carry fixed-point adders (RCA) on look-up table (LUT) based FPGAs. The objective is to transform the given RCA Boolean network into an optimized circuit netlist that can implement the desired functionality with minimum cost. We particularly focus on 6-input LUTs that are inherent in all the modern day FPGAs. Technology dependent optimizations are carried out to utilize this FPGA primitive efficiently and the result is compared against various adder designs. The implementation targets the XC5VLX30-3FF324 device from Xilinx Virtex-5 FPGA family. The cost of the circuit is expressed in terms of the resources utilized, critical path delay and the amount of on-chip power dissipated. Our implementation results show a reduction in resources usage by at least 50%; increase in speed by at least 10% and reduction in dynamic power dissipation by at least 30%. All this is achieved without any technology independent (architectural) modification.

*Index Terms*— FPGA, LUT, FPGA primitives, Technology mapping, Boolean Network.

Original Research Paper DOI: 10.7251/ELS1519014K

#### I. INTRODUCTION

**F**IELD programmable gate arrays provide an alternative approach to application specific integrated circuits (ASIC) implementation [1] with features like large-scale integration, design verification post production, lower non-recurring engineering (NRE) costs, reconfigurable design approach etc. [2, 3]. FPGAs also offer an attractive platform for development of novel systems for rapid system prototyping and low to medium volume productions [1, 4, 5, 6]. Most of the modern day FPGA devices contain programmable logic blocks that have look-up table (LUT) as the basic programmable logic element [7, 8]. A k-input LUT is a digital memory that can implement any Boolean function of k variables. The k inputs in an LUT address 2k storage elements that store the truth table of the Boolean function. LUT based FPGAs account for a significant part of the commercial FPGA market [9, 10].

Since their genesis in 1985 [10], FPGAs have evolved enormously with state-of-art devices having in-built full custom processing elements like multipliers, DSP blocks, fast carry chains, high speed clocking, I/O resources etc. [11, 12, 13]. These blocks are highly optimized in terms of speed or area thereby facilitating efficient realization of complex functions [14, 15]. One of the major changes in the FPGA architecture has been the introduction of 6-input LUT as a logic element [11, 16]. With this FPGA primitive, the logic implementation would lead to higher logic densities resulting in a minimal-depth circuit and hence higher speed - a trend towards which the current FPGAs are oriented [17, 18, 19].

Perhaps the biggest issue with 6-input LUTs is their underutilization while implementing a particular logic function, since many logic functions do not require six inputs [10]. This leads to low logic density and thus slower structures. Although many FPGA vendors have designed these elements with dual output capabilities [17, 18], their usage in implementing a Boolean function still remains far from the optimum.

Another issue is regarding the technology mapping of Boolean networks representing a combinational function. Logic synthesis in FPGAs has a well-defined flow that starts with design entry and proceeds through phases like synthesis, translation, mapping and place and route (PAR). Technology mapping is one of the most important phases in the FPGA computer aided design (CAD) flow that is directly concerned with selecting the circuit elements that will implement a given Boolean network [1, 7]. For LUT based FPGAs the target circuit element is the k-input LUT. Technology mapping is always cost driven. The goal is to produce a minimum-cost circuit that implements a desired Boolean function [1, 7, 8]. The cost of the circuit is typically a measure of its area, speed, power or a combination of these and accordingly there are algorithms that drive the technology mapping process towards area optimization [19, 20, 21, 22, 23, 24], delay optimization

Manuscript received 30 October 2014. Received in revised form 27 March 2015. Accepted for publication 10 May 2015.

Burhan Khurshid is with the Department of Computer Science and Engineering, NIT, Srinagar, India (phone: +91-9797875163; e-mail: burhan\_07phd12@nitsri.net).

Roohie Naaz is with Faculty of Computer Science and Engineering, NIT, Srinagar, India (e-mail: naaz310@nitsri.net).

[25, 26, 27, 28, 29, 30], power optimization [31, 32, 33, 34, 35, 36], or area and delay optimization [37, 38, 39, 40, 41].

Modern day commercially available tools from leading vendors like Xilinx and Altera have fully automated technology mapping. The technology mappers in these tools take the native generic circuit (NGC) file from synthesis and create a native circuit description (NCD) file as per the desired cost function. The NCD file contains the physical description of design in terms of the components in the target device. Thus the mapping process is fully automated and the designer has no control over the selection of circuit elements that will implement the given function.

In this paper, we aim at tackling these two issues. The contributions of this paper are:

- i) We re-design the initial Boolean network for RCA based adders for area, speed, and power optimality. Achieving area and power optimality for Boolean networks with inputs greater than four is NP-hard [31, 42, 43], however, since the basic cell in RCA based fixed point adders is very simple our approach simultaneously addresses the area, speed and power issues and a complete utilization of 6-input LUTs is assured. We do not particularly use any of the algorithms listed previously but our approach uses a combination of techniques like node decomposition, exploiting re-convergent nodes, logic replication etc.

- ii) Since design entry is the only manual phase in the FPGA design flow, we try to control the mapping of the Boolean networks at the design entry step only. This involves modifying the coding style and writing VHDL codes for optimized Boolean networks based on direct instantiations of the targeted circuit elements. This is in contrast to the conventional coding styles that are typically behavioral and rely completely on the synthesizer to map the Boolean network by inferring the logic.

We have compared our implementation results against various adder designs listed in [44]. Our implementation results show a reduction in resources usage by at least 50%; increase in speed by at least 10% and reduction in dynamic power dissipation by at least 30%. We have also compared our implementation against the Xilinx IP adder v 11.0 and a subsequent improvement in performance is observed.

The rest of the paper is organized as follows. Section II discusses some basic terminology used in this paper. Section III discusses the basic technology mapping of the Boolean network corresponding to the RCA cell on LUTs. In section IV we redesign the initial Boolean network to ensure proper utilization of the 6-input LUT. Synthesis and implementation is carried out in section V. Conclusions are drawn in section VI. References are listed at the end.

#### II. DEFINITIONS AND TERMINOLOGY

A *Boolean network* is a directed acyclic graph (DAG) with *nodes* corresponding to logic gates, primary inputs and primary outputs and directed edges corresponding to wires connecting the gates. Since the Boolean networks considered in this paper are simple full-adder circuits, we will use actual gates for nodes. Further the term *network* will be used to refer to a Boolean network representing a combinational function

and the term *circuit* will be used to refer to a Boolean network representing a circuit net-list i.e. a network of connected LUTs.

A node in a network may be driven by zero or more predecessor nodes known as *fan-in* nodes and may drive zero or more successor nodes known as *fan-out* nodes. The primary inputs (PIs) of the network are nodes without any fan-in. Similarly primary outputs (POs) are nodes without any fan-out. A network is said to be *k-bounded* if the number of fan-ins of each node does not exceed *k*.

The *level* of a node is the length of the longest path from any PI to the node. The node itself is counted in the path length. In this paper we have considered buffered inputs and outputs so that PIs and POs also contribute to the network *depth* which is defined as the largest level of a node in the network. The delay and area of a mapped circuit is measured by the depth and number of LUTs respectively.

A *cone* of a node v,  $C_v$ , is a sub-graph consisting of the node v and some of its non-PI predecessors, such that any node in this cone has a path to the node v that lies entirely in  $C_v$ . Node v is referred to as the *root* of the cone.

#### III. MAPPING THE BASIC RCA CELL

Addition is one of the basic operations in digital signal processing (DSP) systems. It is used as a primitive operation in various arithmetic circuits like multipliers, multiply-adders etc. In order to maximize the performance of the adder circuit various technology independent (architectural) approaches have been used. However, this work focuses on carrying out the technology dependent optimization of the conventional ripple carry adder on LUT based FPGAs.

Technology mapping using LUTs is a two step process. In the first step, the entire network is partitioned into suitable sub-networks. The individual nodes within each sub-network are then covered with suitable cones. The logic implemented by each cone is then mapped onto a separate LUT and an optimal LUT net-list is obtained. In the second step, the netlist for the entire network is constructed by assembling the individual net-lists. The overall goal is to have a circuit implementation that uses minimum possible LUTs and has minimum possible depth.

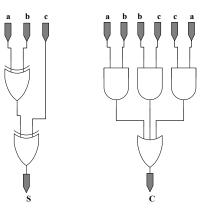

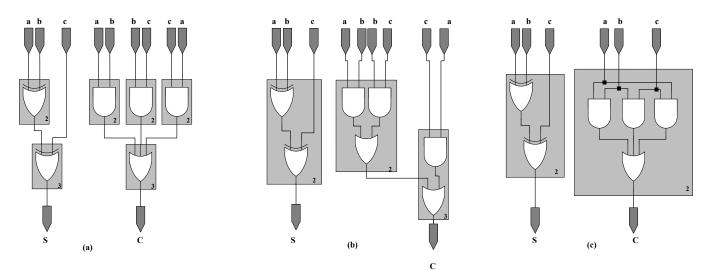

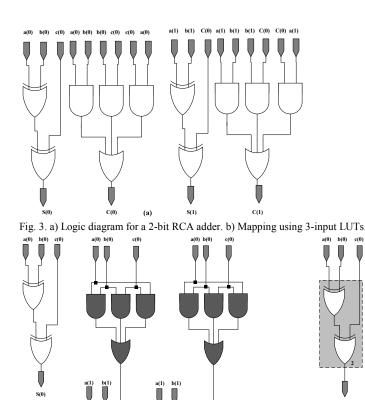

The basic cell in an RCA network is a full adder. Fig. 1 shows the Boolean network for a full adder circuit. The network is partitioned into two sub-networks corresponding to sum (S) and carry (C), by dividing it at fan-out nodes. Each sub-network is separately mapped into a circuit of LUTs by covering the individual nodes with suitable cones. A straight forward approach would be to cover each node within a subnetwork with a separate cone. The sub-network is then traversed in post-order depth-first fashion and each cone is assigned to a separate LUT as shown in Fig. 2(a). The number at the lower-right corner of each LUT indicates the level of the LUT assuming each LUT has a delay of one unit. The overall depth of the circuit at PO nodes S and C is four (including the buffers at PIs and POs). The total number of LUTs needed is six. The number of LUTs may be reduced by decomposing the 3-input OR gate in the carry sub-network. The decomposed node is included in two separate cones and the sub-network is

again traversed in post-order depth-first fashion to have a circuit implementation of Fig. 2(b). The number of LUTs is now reduced to three. However, an optimal implementation may be obtained by exploiting the reconvergent PI nodes in the carry circuit. Reconvergent nodes share the same inputs and can be exploited to reduce the number of PIs to a subnetwork. This is shown in Fig. 2(c) where the reconvergent paths are included within the LUTs and the circuit is implemented with a single LUT for each sum and carry subnetwork. The number of LUTs utilized is two and the overall depth including the buffers at PIs and POs is three. An n-bit adder implemented using the optimized circuit of Fig. 2(c) will have an overall depth of n+2 and will require 2n LUTs.

Fig. 2. Mapping of the RCA cell. a) Direct Mapping. b) Mapping The following instantiations were used in the design entry phase to map the circuit in Fig. 2(c).

begin

```

-- Optimal mapping for sum output

L_1 : LUT3_L generic map (INIT => X"96")

port map (S, c, b, a);

-- Optimal mapping for carry output

L_2 : LUT3_L generic map (INIT => X"E8")

port map (C, c, b, a);

```

end Behavioral;

#### IV. OPTIMAL MAPPING FOR 6-INPUT LUT

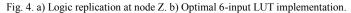

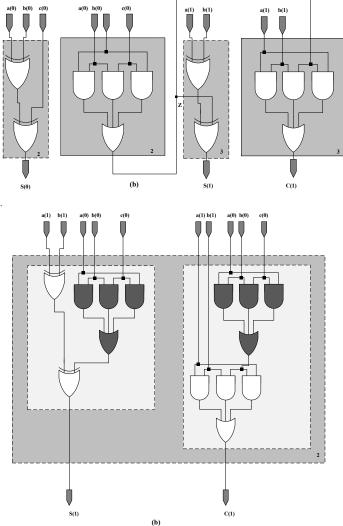

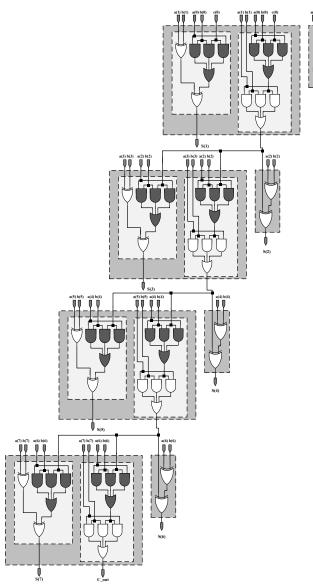

The circuit in Fig. 2(c) may be an optimal circuit for a 3input LUT but when the target element is a 6-input LUT, it leads to severe under-utilization of the resources resulting in a low-density circuit. Since most of the modern day FPGAs have 6-input LUTs as their basic logic element, it is compelling to devise a method that utilizes this circuit element efficiently. We counter this issue by considering two RCA cells simultaneously and restructuring the initial Boolean network so that the circuit obtained after transformation utilizes the targeted 6-LUT efficiently. Fig. 3(a) shows the Boolean network that corresponds to two full adder cells. The network using node decomposition c) Mapping exploiting reconvergent nodes. may be partitioned into three separate sub-networks corresponding to two sum bits S(0) and S(1) and a carry bit C(1). The reconvergent nodes in the carry sub-network are exploited to reduce the number of inputs and a circuit implementation similar to Fig. 2(c) is obtained. This is shown in Fig. 3(b). However, an optimal 6-input LUT implementation may be achieved by replicating the logic at fan-out node Z as shown in Fig. 4(a). The replicated nodes are shown by shaded portions. Node replication ensures that the sub-networks S(1)and C(1) have the same inputs. The covering process covers the individual networks with suitable cones and each cone is mapped onto a separate LUT. Sub-networks S(1) and C(1) share the same inputs and are implemented using a single 6-LUT with dual outputs. The overall circuit is shown in Fig. 4(b). The depth of the circuit is three and the number of LUTs utilized is two. An n-bit adder implemented using this circuit will have an overall depth of (n/2)+2 and will utilize only n LUTs. Thus the implementation based on Fig. 4(b) is theoretically 50% more efficient than the one based on Fig. 2(c). Fig. 5 shows an 8-bit adder unit constructed using the optimized circuit of Fig. 4(b).

(a)

The following instantiations were used in the design entry phase to map the circuit in Fig. 4(b).

```

begin

-- Optimal mapping for S(0) output

L_1: LUT3_L generic map (INIT => X"96")

port map (S(0), c(0), b(0), a(0));

-- Optimal mapping for S(1) and C(1) output

L_2: LUT6_2 generic map (INIT => X"E81717E8FFE8E800")

port map (C(1), S(1), c(0), b(0), a(0), b(1), a(1), '1');

end Behavioral;

```

#### V. SYNTHESIS AND IMPLEMENTATION

#### A. Methodology

The implementation in this work targets the XC5VLX30-3FF324 device from Xilinx Virtex-5 FPGA family. The implementation is carried out for an input word-length varying from 8 to 64 bits. The parameters considered are area, timing and dynamic power dissipation. Area is considered in terms of the number of occupied slices. Timing analysis may be static or dynamic. Static timing analysis gives information about the delay associated with the critical path and the maximum frequency at which the design may be operated. Dynamic timing analysis verifies the functionality of the design by

applying test vectors and checking for correct output vectors. Dynamic timing analysis is done post implementation and PAR. The quality of dynamic timing analysis depends on the number of test vectors used. An important result from dynamic timing analysis is the switching activity information (toggle rates, signal rates etc.). This information is captured in the value charge dump (VCD) file and helps in determining accurate power measurements. Dynamic power dissipation is related to the charging and discharging of various node capacitances along different switching elements. To ensure a fair comparison, similar test benches have been used for all the implemented designs i.e. the input statistics remain same in each case. The initial design entry is done using VHDL through direct instantiation of the primitives rather than writing inferential codes and letting the synthesizer decide how to infer the logic. This ensures a fairly controlled mapping. The constraints relating to synthesis and implementation are duly provided and a complete timing closure is ensured in each case. The design synthesis and implementation is carried out in Xilinx ISE 12.1 [45] and the simulator database is then analyzed for speed and area metrics. Power metrics are obtained from Xpower analyzer.

Fig. 5. 8-bit adder structure based on technology optimized binary adder cell.

#### B. Experimental results

We have compared our implementation results against the various fixed point adder designs in [44] and the Xilinx IP adder v 11.0.

| TABLE I                                                          |

|------------------------------------------------------------------|

| RESOURCE UTILIZATION FOR DIFFERENT ADDERS ON XC5VLX30 FOR 16 BIT |

| INDUT WORD I ENCTU                                               |

| Adder Design                      | No. of occupied slices |

|-----------------------------------|------------------------|

| Carry chain adder (CCA) [44]      | 9                      |

| Carry select adder (CSA) [44]     | 7                      |

| Carry skip adder (CKA) [44]       | 7                      |

| Carry look ahead adder (CLA) [44] | 16                     |

| Sign magnitude adder (SMA) [44]   | 15                     |

| Xilinx IP adder v.11.0            | 4                      |

| 3-input LUT based adder (LUT_3)   | 7                      |

| 6-input LUT based adder (LUT_6)   | 3                      |

Table I gives the comparison of resource utilization for various adder designs. The comparison is carried out for an

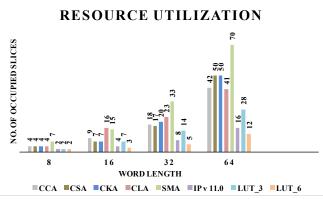

input word-length of 16 bits. It is observed that technology mapping using LUTs results in a subsequent reduction of the on-chip resources being utilized. The most area efficient structure is obtained using 6-input LUT because of its ability to implement sum and carry sub-networks in a single LUT. Further analysis is carried out for different adders for varying word-lengths. The results are plotted as a function of wordlength and appear in Fig. 6.

Fig. 6. Resource utilization for different adder structures.

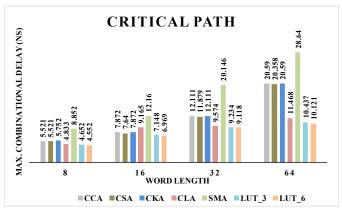

Technology mapping using LUTs also reduces the depth of the implemented circuit resulting in shorter critical paths. Table II provides a comparison of the critical path delay for various adders for an input word-length of 16 bits.

TABLE II CRITICAL PATH DELAY FOR DIFFERENT ADDERS ON XC5VLX30 FOR 16 BIT INPUT WORD-LENGTH

| Adder Design                      | Critical path delay (ns) |

|-----------------------------------|--------------------------|

| Carry chain adder (CCA) [44]      | 7.872                    |

| Carry select adder (CSA) [44]     | 7.64                     |

| Carry skip adder (CKA) [44]       | 7.872                    |

| Carry look ahead adder (CLA) [44] | 9.165                    |

| Sign magnitude adder (SMA) [44]   | 12.16                    |

| 3-input LUT based adder (LUT_3)   | 7.148                    |

| 6-input LUT based adder (LUT_6)   | 6.969                    |

Fig. 7. Critical path delay variation for different adders.

Fig. 7 gives the variation in critical path delay for different adders as word-length is varied from 8 to 64 bits. We have also compared the maximum clock frequency for the 6-LUT based adder and the Xilinx IP adder v 11.0. The results are shown for different word lengths in Table III.

| W/          | Max. Clock frequency | (MHz)    |

|-------------|----------------------|----------|

| Word length | Xilinx IP v 11.0     | LUT_6    |

| 8           | 355.493              | 498.008  |

| 16          | 266.028              | 378.5011 |

| 32          | 211.372              | 287.7934 |

| 64          | 145.65               | 210.32   |

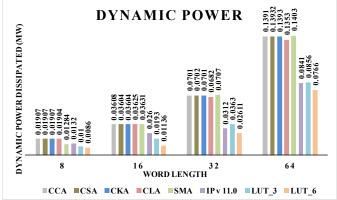

Finally dynamic power dissipation for different structures is considered. The dynamic power dissipation is a function of the input voltage  $(V^2)$ , the clock frequency  $(f_{clk})$ , the switching activity ( $\alpha$ ), the total capacitance seen by a particular node  $(C_L)$  and the number of elements used  $(\sigma)$ . The capacitance  $C_L$ . which needs to be driven at each toggling node, varies with the type, fan-out, and capacitance of the logic and routing resources used in the design. The use of LUTs ensures that the high activity switching nodes remain hidden. This reduces the charging and discharging of the capacitances associated with these nodes, resulting in reduced dynamic power dissipation. In addition, there is also a reduction in the number of elements  $(\sigma)$  being utilized which reduces the power dissipated in the logic. The analysis is done for a constant supply voltage and at maximum operating frequency for each structure. To ensure a reasonable comparison the test vectors provided during post route simulations are selected to represent the worst case scenario for data coming into the adders. Same test bench is used for all the synthesized structures. The design node activity captured in the VCD file along with the power constraint file (PCF) is used for power analysis in the Xpower analyzer tool. Table IV shows the comparison of dynamic power dissipation for various adders for an operand length of 16 bits.

Further analysis is carried out by plotting the total dynamic power dissipation as a function of input word-length for different adders. The result is shown in Fig. 8.

TABLE IV DYNAMIC POWER DISSIPATION FOR DIFFERENT ADDERS ON XC5VLX30 FOR 16 BIT INPUT WORD-LENGTH

| Adder Design                      | Dynamic<br>dissipation (Watt) | power |

|-----------------------------------|-------------------------------|-------|

| Carry chain adder (CCA) [44]      | 0.03608                       |       |

| Carry select adder (CSA) [44]     | 0.03604                       |       |

| Carry skip adder (CKA) [44]       | 0.03604                       |       |

| Carry look ahead adder (CLA) [44] | 0.03625                       |       |

| Sign magnitude adder (SMA) [44]   | 0.03631                       |       |

| Xilinx IP adder v.11.0            | 0.026                         |       |

| 3-input LUT based adder (LUT_3)   | 0.0193                        |       |

| 6-input LUT based adder (LUT_6)   | 0.01136                       |       |

Fig. 8. Variation in Dynamic power dissipation with word-length.

#### VI. CONCLUSION